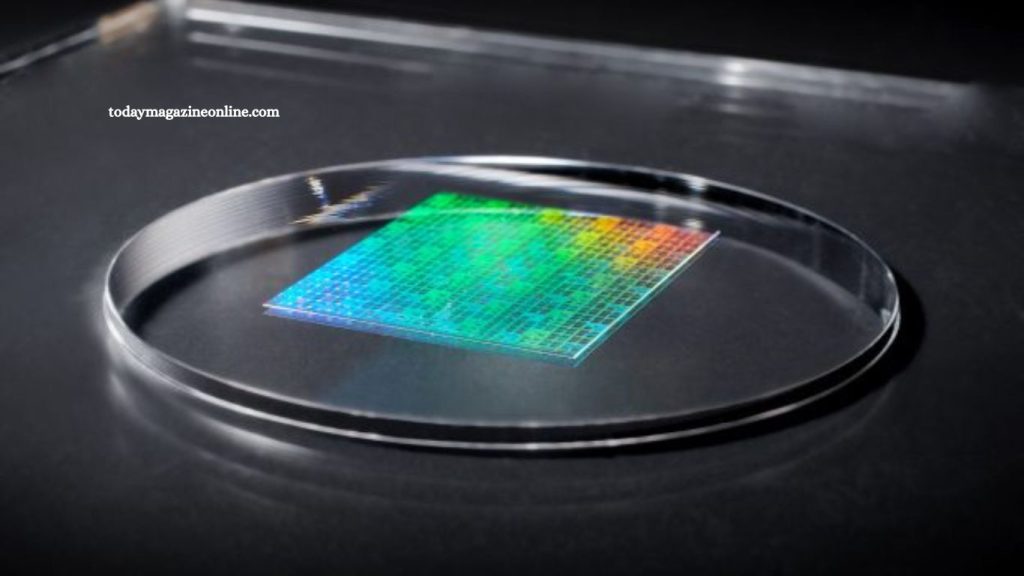

Tokyo, Japan — Dai Nippon Printing (DNP) has announced a breakthrough in semiconductor manufacturing with the successful development of nanoimprint lithography (NIL) technology capable of producing circuit patterns as fine as 10 nanometers. Designed for patterning 1.4nm-class logic semiconductor circuits, the technology is already undergoing customer evaluation, with mass production targeted for 2027.

DNP expects this innovation to support the ongoing miniaturization of advanced logic chips used in smartphones, data centers, NAND Flash, and other applications.DNP plans to demonstrate the 10nm-linewidth NIL technology at SEMICON Japan 2025, to be held at Tokyo Big Sight.

Read More: NVIDIA Rises After Deal to License Groq’s Chip Technology

Addressing the Challenges of EUV Lithography

As semiconductor performance requirements continue to grow, demand for advanced logic nodes has surged, driving improvements in extreme ultraviolet (EUV) lithography. However, EUV presents significant challenges: it requires massive capital investments, involves complex fabrication processes, and generates high energy consumption with associated environmental impacts.

Nanoimprint Lithography: A Viable Alternative

Since 2003, DNP has been developing nanoimprint technology, which directly imprints circuit patterns onto substrate materials. This approach offers an alternative pathway for chipmakers, potentially reducing energy consumption in lithography and optimizing costs in certain process steps.

The newly developed 10nm-linewidth NIL technology can partially replace EUV lithography in selected patterning stages. This is particularly valuable for semiconductor manufacturers who have yet to deploy EUV tools, providing another option for advanced logic production. Moreover, ultra-fine manufacturing using NIL can reduce lithography energy consumption to roughly one-tenth of current mainstream processes.

Industry Engagement and Future Outlook

DNP is actively engaging with semiconductor manufacturers and has initiated evaluation programs for the new NIL technology. The company plans to expand production capacity in line with anticipated market growth, positioning nanoimprint lithography as a key driver of growth within its semiconductor segment.

By offering a cost-effective and energy-efficient alternative to EUV lithography, DNP’s 10nm NIL technology could play a significant role in the next generation of high-performance semiconductor devices.

Frequently Asked Questions

What is DNP’s 10nm NIL technology?

A nanoimprint lithography method that creates 10nm circuit patterns for advanced logic chips.

How does NIL differ from EUV?

NIL directly imprints patterns, using less energy and cost than EUV lithography.

When will it be available?

Mass production is targeted for 2027.

What are its main benefits?

Lower energy use, reduced cost, and partial replacement of EUV in selected steps.

Who benefits from this technology?

Semiconductor makers producing high-performance chips, especially without EUV tools.

Where will it be showcased?

At SEMICON Japan 2025, Tokyo Big Sight.

Conclusion

Dai Nippon Printing’s development of 10nm nanoimprint lithography represents a significant advancement in semiconductor manufacturing. By offering a cost-effective, energy-efficient alternative to EUV lithography, the technology enables continued miniaturization of high-performance logic chips while reducing environmental impact.